# **RTG4 FPGA DDR Memory Controller User Guide**

# Introduction (Ask a Question)

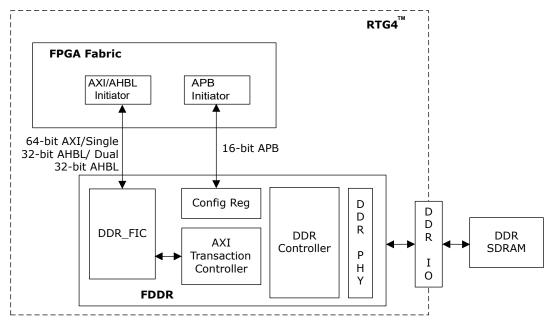

The Fabric DDR (FDDR) subsystem is a hardened Application Specific Integrated Circuit (ASIC) block for interfacing the DDR2, DDR3, and LPDDR1 memories. The RTG4<sup>™</sup> devices have two FDDR blocks. The FDDR subsystem is used to access the DDR memories for high-speed data transfers. It includes the DDR memory controller, DDR PHY, and arbitration logic to support multiple initiators. DDR controller is SEU mitigated and you must not have any performance impact due to SEU events.

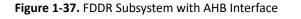

The FPGA fabric initiators communicate with the DDR memories interfaced to the FDDR subsystem through the AXI or AHB interfaces. The FDDR subsystem has an APB target interface to configure the FDDR from the FPGA fabric initiator.

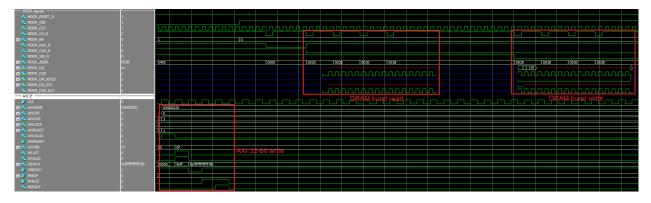

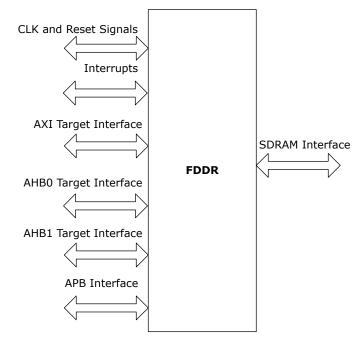

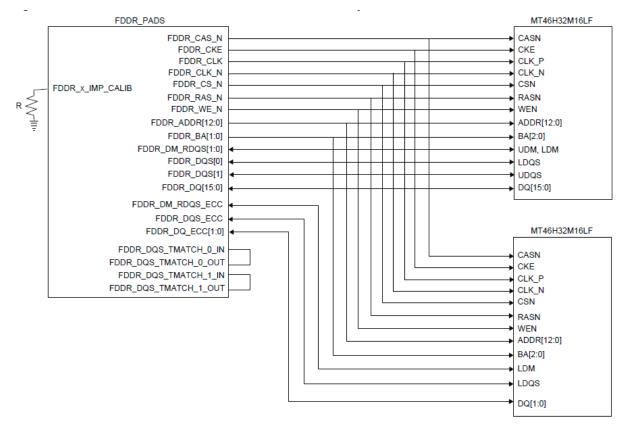

The following figure shows the FDDR subsystem.

Figure 1. System-Level FDDR Block Diagram

The FDDR subsystem accepts data transfer requests from AXI or AHBL interfaces. Any read or write transactions to the DDR memories can occur from the AXI or AHBL initiators in the FPGA Fabric through the DDR\_FIC interface. The FDDR subsystem can also automatically perform DDR initialization, refresh, and ZQ calibration functions.

## Important:

- Libero<sup>®</sup> SoC keeps the unused FDDR subsystems in Reset mode by driving the FDDR Reset signal to 0. The Netlist Viewer in Libero SoC shows the FDDR\_POWER\_DOWN buffers, which keep the unused FDDR blocks in Reset mode.

- The maximum DDR3 data-rate supported by RTG4 FDDR is 333 MHz or 667 Mbps. Therefore, Write Leveling is not mandatory and the interface does work if the board layout includes length matching and follows RTG4 board-level guidelines (see 1.17. Printed Circuit Board Guidelines).

For Read Leveling, Libero SoC auto-generates predefined static delay ratios for FDDR initialization. These delay values are sufficient if the board layout follows the RTG4 board-level guidelines.

## Features (Ask a Question)

The following are the features of the FDDR memory controller:

- Integrated on-chip DDR memory controller and PHY

- Supports LPDDR1, DDR2, and DDR3 memory devices

- Upto 667 Mbps (333 MHz DDR) performance

- Supports memory densities up to 2 GB

- Supports 8, 16, or 32 -bits data bus width modes

- Supports a maximum of 8 memory banks

- Supports a single rank of memory

- Enable or disable Single Error Correction and Double Error Detection (SECDED)

- Supports DRAM burst lengths of 4, 8, or 16, depending on the Bus width mode and the DDR type configured

- · Supports sequential and interleaved burst ordering

- Programs internal control of ZQ short calibration cycles for DDR3 configurations

- Supports dynamic scheduling to optimize bandwidth and latency

- Supports self refresh entry and exit on command

- Supports deep power-down entry and exit on command

- Flexible address mapper logic that enables application specific mapping of row, column, bank, and rank bits

- Configurable support for 1T or 2T timing on the DDR SDRAM control signals

- Supports autonomous DRAM power-down entry and exit caused by lack of transaction arrival for programmable time

# Memory Configurations (Ask a Question)

The RTG4 FDDR subsystem supports a wide range of common memory types, configurations, and densities, as listed in the following table. If SECDED mode is enabled in the FDDR controller, the external memory module must be connected to the following:

- Data lines, FDDR\_DQ\_ECC[3:0] when data width is 32 bits

- Data lines, FDDR\_DQ\_ECC[1:0] when data width is 16 bits

- Data line, FDDR\_DQ\_ECC[0] when data width is 8 bits

#### Table 1. Supported Memory (DDR2, DDR3, and LPDDR1) Configurations

| Memory Depth | Width (in Bits) | Width (in Bits) (in SECDED Mode) | RTG4 <sup>™</sup> Devices |

|--------------|-----------------|----------------------------------|---------------------------|

| 128M         | 32              | 36                               | Yes                       |

|              | 16              | 18                               |                           |

|              | 8               | 9                                |                           |

| 256M         | 32              | 36                               |                           |

|              | 16              | 18                               |                           |

|              | 8               | 9                                |                           |

| 512M         | 32              | 36                               |                           |

|              | 16              | 18                               |                           |

|              | 8               | 9                                |                           |

| 1G           | 32              | 36                               |                           |

|              | 16              | 18                               |                           |

|              | 8               | 9                                |                           |

# Performance (Ask a Question)

The following table lists the maximum data rates supported by each data pin in the FDDR subsystem for the supported memory types. For more information, see the RTG4 FPGA Datasheet.

#### Table 2. DDR Speeds

| Memory Type | Maximum Data Rate (Mbps) |

|-------------|--------------------------|

| LPDDR1      | 266 (133 MHz)            |

| DDR2        | 66 (333 MHz)             |

| DDR3        | 667 (333 MHz)            |

# I/O Utilization (Ask a Question)

The following table lists the I/O utilization for RTG4 devices corresponding to the supported DDR bus widths. The remaining I/Os in the banks can be used for general purposes.

## Important:

- If the FDDR subsystem is configured for LPDDR, one more I/O is also available for every 8 bits as the LPDDR does not have the FDDR\_DQS\_N pin.

- The AL40 and AE41 pins cannot be used with output register (OUT\_REG) and enable register (EN\_REG) of the I/O if FDDR\_E is not used. The AL2 and AE1 pins cannot be used with OUT\_REG or EN\_REG if FDDR\_W is not used.

- For general purpose usage of the unused I/Os of the FDDR bank, select one of the I/O standards with the voltage level same as that of the DDR I/Os.

- Self refresh must be disabled if the FDDR banks contain I/Os that are used for both DDR and for general purpose fabric I/Os. For more information, see 1.15.2. Self Refresh.

#### Table 3. I/O Utilization for RTG4 Devices

| FDDR Bus Width       | FDDR_E               | FDDR_W               |

|----------------------|----------------------|----------------------|

| 36 bits <sup>1</sup> | Bank 0 (85 + 1 pin)  | Bank 9 (85+1 pin)    |

| 32 bits <sup>1</sup> | Bank 0 (76 + 1 pin)  | Bank 9 (76+1 pin)    |

| 18 bits <sup>2</sup> | Bank 0 (59 + 5 pins) | Bank 9 (59 + 5 pins) |

| 16 bits <sup>2</sup> | Bank 0 (53 + 5 pins) | Bank 9 (53 + 5 pins) |

| continued           |                      |                      |

|---------------------|----------------------|----------------------|

| FDDR Bus Width      | FDDR_E               | FDDR_W               |

| 9 bits <sup>2</sup> | Bank 0 (47 + 5 pins) | Bank 9 (47 + 5 pins) |

| 8 bits <sup>2</sup> | Bank 0 (41 + 5 pins) | Bank 9 (41 + 5 pins) |

#### Important:

- 1. In 36 or 32 bit DDR bus width mode, an additional pin is reserved. For FDDR\_E, the reserved pin is Bank 0- AK35; for FDDR\_W, the reserved pin is bank9-AK7.

- 2. In 18, 16, 9, or 8 -bits DDR bus width mode, five additional pins are reserved. For FDDR\_E, the reserved pins (Bank 0) are AK35, AJ31, AK32, AK33, AL35 and for FDDR\_W, the reserved pins (Bank 9) are AK7, J11, AK9, AK10, and AL7.

# I/O Standards (Ask a Question)

The following table lists the supported I/O standards for different DDR memories.

#### Table 4. Supported I/O Standards for Different DDR Memories

| Memory Type | I/O Standards     |

|-------------|-------------------|

| DDR3        | SSTL15I, SSTL15II |

| DDR2        | SSTL18I, SSTL18II |

| LPDDR       | LVCMOS18          |

# **Table of Contents**

| Inti | roduction                                                                       | 1   |

|------|---------------------------------------------------------------------------------|-----|

|      | Features                                                                        | 2   |

|      | Memory Configurations                                                           | 2   |

|      | Performance                                                                     |     |

|      | I/O Utilization                                                                 |     |

|      | I/O Standards                                                                   | 4   |

| 1.   | Functional Description                                                          | 7   |

|      | 1.1. Clock Controller                                                           | 7   |

|      | 1.2. DDR_FIC                                                                    | 8   |

|      | 1.3. DDR Bridge                                                                 | 9   |

|      | 1.4. AXI Transaction Controller                                                 | 12  |

|      | 1.5. DDR Controller                                                             | 13  |

|      | 1.6. DDR PHY                                                                    | 21  |

|      | 1.7. Initialization                                                             | 21  |

|      | 1.8. FDDR Subsystem Ports                                                       | 27  |

|      | 1.9. Functional Timing Diagrams                                                 |     |

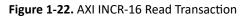

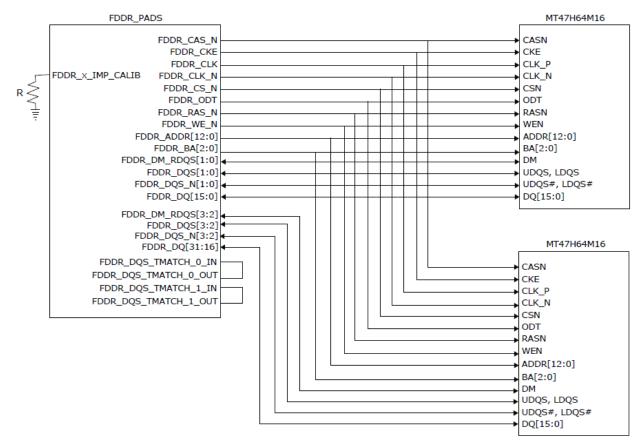

|      | 1.10. DDR Memory Device Examples                                                |     |

|      | 1.11. Implementing and Configuring FDDR Subsystem                               |     |

|      | 1.12. Simulating FDDR Subsystem                                                 |     |

|      | 1.13. Functional Examples                                                       |     |

|      | 1.14. Synthesis Recommendations, Timing Constraints, and Floor Plan Constraints |     |

|      | 1.15. Low Power Operating Options                                               |     |

|      | 1.16. FDDR Subsystem Performance Optimization                                   |     |

|      | 1.17. Printed Circuit Board Guidelines                                          |     |

|      | 1.18. Debugging Techniques                                                      | 55  |

| 2.   | FDDR Configuration Registers                                                    | 57  |

|      | 2.1. DDR Controller Configuration Register Summary                              |     |

|      | 2.2. DDR Controller Configuration Register Bit Definitions                      | 60  |

|      | 2.3. PHY Configuration Register Summary                                         | 86  |

|      | 2.4. PHY Configuration Register Bit Definitions                                 | 87  |

|      | 2.5. DDR_FIC Configuration Registers Summary                                    |     |

|      | 2.6. DDR_FIC Configuration Register Bit Definitions                             |     |

|      | 2.7. FDDR SYSREG Configuration Register Summary                                 | 94  |

|      | 2.8. FDDR SYSREG Configuration Register Bit Definitions                         | 95  |

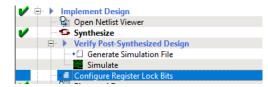

| 3.   | Appendix: Register Lock Bits Configuration                                      | 101 |

|      | 3.1. Lock Bit File                                                              |     |

|      | 3.2. Lock Bit File Syntax                                                       |     |

|      | 3.3. Locking and Unlocking a Register                                           |     |

| 4.   | Revision History                                                                |     |

| Міс  | rochip FPGA Support                                                             |     |

|      |                                                                                 |     |

| Mic  | rochip Information                                                              |     |

|      | The Microchip Website                                                           | 105 |

| Product Change Notification Service                     | . 105                   |

|---------------------------------------------------------|-------------------------|

| Customer Support                                        |                         |

| Microchip Devices Code Protection Feature               |                         |

| Legal Notice                                            | . 106                   |

| Trademarks                                              |                         |

| Quality Management System                               | . 107                   |

| Worldwide Sales and Service                             |                         |

| Legal Notice<br>Trademarks<br>Quality Management System | . 106<br>. 106<br>. 107 |

# 1. Functional Description (Ask a Question)

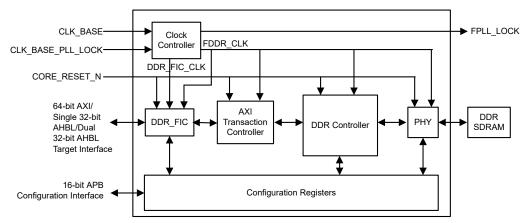

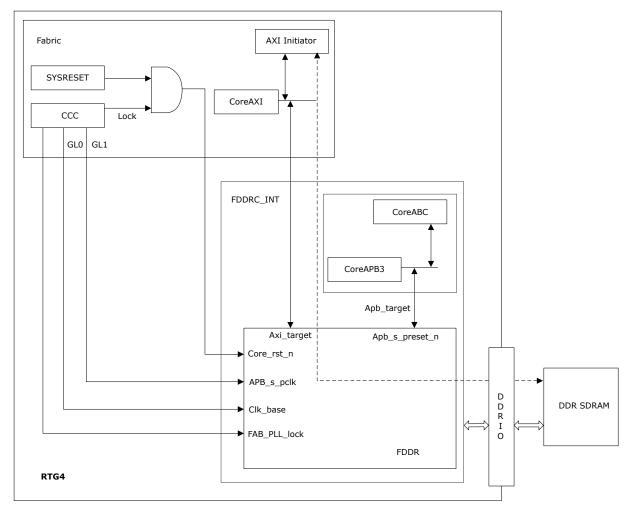

The following figure shows the functional block diagram of the FDDR subsystem. The main components include the clock controller, DDR fabric interface controller (DDR\_FIC), AXI transaction controller, DDR memory controller, and DDR PHY.

Figure 1-1. FDDR Subsystem Functional Block Diagram

## 1.1 Clock Controller (Ask a Question)

The FDDR subsystem has a dedicated clock controller that generates aligned clocks to all the FDDR sub-blocks for proper operation and synchronous communication with the user logic in the FPGA fabric. The base clock (CLK\_BASE) for the FDDR subsystem comes from a fabric Clock Conditioning Circuitry (CCC) or an external source through the FPGA fabric. The FDDR clock controller is associated with a dedicated Fabric Phase-Locked Loop (FPLL) for clock synthesis and deskewing the internal DDR\_FIC clock from the base clock.

The FDDR clock controller consists of an FPLL and Fabric Alignment Clock Controller (FACC).

### 1.1.1 FPLL (Ask a Question)

FPLL is a Radiation Tolerant PLL (RT-PLL) and it ensures that the clock outputs from PLL do not have glitches or have significant differences in jitter when exposed to radiation. The CLK\_BASE signal from the FPGA fabric is used as a reference clock to the FPLL and is multiplied to generate a clock frequency of upto 333 MHz. The base clock can be generated from any one of the fabric CCCs or a clock source (internal or external) through global network.

The device core supply (VDD) powers the digital section, and the analog supply (FDDR\_PLL\_VDDA) powers the analog section. The required voltage for FDDR\_PLL\_VDDA is 3.3V, and this does not impact the FPLL frequency range. See the RTG4 FPGA Datasheet for the FPLL operational range and characteristics.

FPLL generates a lock signal (FPLL\_LOCK) to indicate that is locked onto the CLK\_BASE signal. The precision of FPLL\_LOCK discrimination can be adjusted using the lock window controls. It represents the phase error window for lock assertion. The lock window can be adjusted between 500 parts per million (ppm) and 64,000 ppm in powers of 2. The integration of the lock period can be adjusted using a built-in lock counter. The lock counter or lock delay indicates the number of reference clock cycles to wait after FPLL is locked to assert the FPLL\_LOCK signal. The lock delay is used to avoid false toggling of the FPLL lock signal. The lock counter can be configured between 32 and 1048576 cycles in powers of 2.

## 1.1.2 FACC (Ask a Question)

Within the FDDR clock controller, FACC is responsible for interfacing with FPLL, generating the aligned clocks required by the FDDR subsystem, and controlling the alignment of FPGA fabric interface clocks.

The clocks generated by FACC are:

- **FDDR\_CLK**: Clocks the FDDR subsystem. FDDR\_CLK can be operated up to 333 MHz, depending on the type of DDR present in the system.

- **DDR\_FIC\_CLK**: Clocks the DDR\_FIC, and defines the frequency at which the connected FPGA Fabric subsystem operates.

- **FACC Divider**: Divides the high-speed clock coming from the FPLL to generate the DDR\_ FIC clock according to the configured division ratios. The possible FDDR\_CLK:DDR\_FIC\_CLK ratios are 1:1 to 16:1.

#### 1.1.3 FPLL Initialization (Ask a Question)

To attain clock alignment between the FPGA fabric and the FDDR subsystem, FPLL must be used to perform deskewing of the FDDR clocks. After FPLL is initialized, it typically takes over 500 divided reference clock cycles for the lock to be achieved. The FPLL lock assertion time is also dependent on the FPLL lock parameters (lock window and lock delay). There is no provision made for operation of the FDDR subsystem except the APB interface, before the FPLL lock is achieved.

## 1.1.4 PLL Lock Monitoring (Ask a Question)

FDDR has an input, CLK\_BASE\_PLL\_LOCK, to monitor the fabric PLL lock. It must be connected to the lock signal generated by the fabric PLL that is used to generate the base clock to the FDDR.

Within the FDDR subsystem, there are two interrupts related to the PLL lock. A lock interrupt, indicates that the FPLL lock is achieved, and further FPLL lock lost the interrupt. Each of these two interrupts has a corresponding interrupt enable bit in the FDDR subsystem registers. It is also possible to read the state of the two PLL lock signals from the FDDR registers.

In the event of loss of FPLL lock, even if the output is not exactly in phase lock with the reference, FPLL still generates a clock. User logic in the FPGA fabric can use the FPLL\_LOCK signal to prevent communication with the FDDR subsystem during this time.

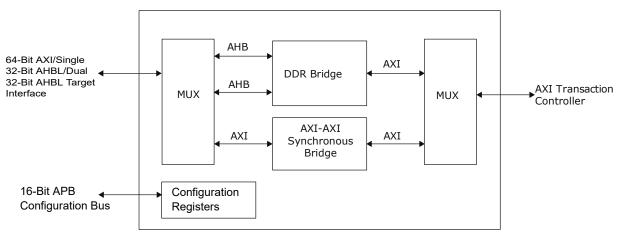

## 1.2 DDR\_FIC (Ask a Question)

DDR\_FIC facilitates communication between the FPGA fabric initiators and the AXI transaction controller. The following figure shows the DDR\_FIC block diagram.

Figure 1-2. DDR\_FIC Block Diagram

Fabric initiators can access the FDDR subsystem using the following:

- A single AXI-64 bit interface

- A single AHBL-32 bit interface

- Dual AHBL-32 bit interfaces

If the AXI-64 interface is selected, DDR\_FIC acts as an AXI to AXI synchronous bridge. In this mode, the FPGA fabric initiator can perform locked transactions. For this purpose, a user configurable 20 bit down counter keeps track of the duration of the locked transfer. If the transfer is not completed before the down counter reaches zero, a single clock cycle pulse interrupt is generated from DDR\_FIC to the fabric interface.

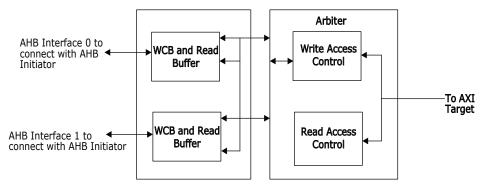

If single or dual AHBL-32 bit interface is selected, DDR\_FIC converts the single or dual 32 bit AHBL initiator transactions from the FPGA fabric to the 64 bit AXI transactions. The DDR bridge, which is embedded as part of DDR\_FIC, is enabled in this case. The DDR bridge has an arbiter that uses a round robin priority scheme on read and write requests from the two AHB initiators.

The DDR\_FIC input interface is clocked by the FPGA fabric clock, and the AXI transaction controller is clocked by FDDR\_CLK from the FDDR clock controller. Clock ratios between FDDR\_CLK and DDR\_FIC clocks can vary. Supported ratios are from 1:1 to 16:1. Clock ratios can be configured using the Libero SoC software or through the FDDR\_FACC\_DIVISOR\_RATIO register. For more information, see Table 2-105.

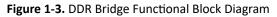

## 1.3 DDR Bridge (Ask a Question)

The DDR bridge facilitates multiple AHB bus initiators to access a single AXI target and optimizes read and write operations from multiple AHB initiators to a single external DDR memory.

The DDR bridge consists of two main components: Read Combining Buffers (RCB) and Write Combining Buffers (WCB), and an arbiter, as shown in the following figure. The DDR bridge buffers the AHB write transactions into write combining buffers before bursting out to the external DDR memory. It also includes read buffers for AHB initiators to efficiently read data from the external DDR memory. All buffers within the DDR bridge are implemented with latches and so are not subject to Single Event Upsets (SEUs). The external DDR memory regions can be configured to be non-bufferable. If an initiator interface requests a write or read to a non-bufferable region, the DDR bridge is bypassed. The size of the non-bufferable address space can also be configured.

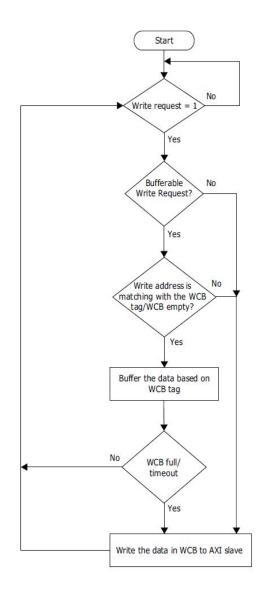

## 1.3.1 Write Combining Buffer (Ask a Question)

WCB combines multiple write transactions from the AHB initiator into the AXI burst transactions. It has a user configurable burst size of 16 or 32 bytes. Each WCB maintains a base address tag that stores the base address of the data to be combined in the buffer.

For each write transaction, the address is compared with the WCB tag. If the address matches the tag, data is combined into the buffer. WCB writes to the appropriate byte location based on the offset address of the data. It can also be disabled, if buffering is not required.

WCB has a 10 bit timer (down counter) that starts when the first bufferable write data is loaded into it. The timer starts decrementing at every positive edge of the AHB clock and when it reaches zero, the data in WCB is written to the AXI target.

WCB checks for any other initiator that has initiated a read operation to the same address for which data is already present in a write buffer or for which a write operation is in progress. If the address for a read request matches the write buffer tag, the read request is held until the buffer is written completely to the AXI target.

The following figure shows the flowchart for WCB operation.

Figure 1-4. WCB Operation

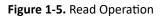

#### 1.3.2 Read Buffer (Ask a Question)

The DDR bridge has a read buffer for each initiator to hold the fetched DDR burst data. Each read buffer has a configurable burst size of 16 or 32 bytes. The read buffer initiates a DDR burst size request for reads in the bufferable region, regardless of the size of request from the initiator. Each read buffer is associated with a specific initiator for reading. It does not check the read addresses of other initiators to determine whether that data can be read from the read buffer. There is no cross buffer read access.

The following figure shows the flowchart for read operation.

The read buffer is invalidated under the following conditions:

- If the address from the initiator is outside the tag region, the current data in the read buffer is invalidated.

- To ensure proper data coherency, all initiator's write addresses are tracked. If an address matches that of the read buffer tag, the read entry is invalidated.

- A non-bufferable or locked transaction is initiated by any initiator.

- An Invalidate command is issued.

- A buffer disable command is issued.

- An error response from DDR for the expected word read.

## 1.3.3 Arbiter (Ask a Question)

The DDR bridge arbiter includes two independent arbitration controllers for read and write requests.

## 1.3.3.1 Write Access Controller (Ask a Question)

The Write Access Controller (WAC) arbitrates write requests from the WCBs and grants access to one of the requesting initiators based on its priority. A round robin priority scheme is applied between

Initiator Interface 0 and Initiator Interface 1. All transactions from a single initiator have a dedicated initiator ID.

Once a burst transaction is initiated to the external DDR memory, the transactions are completed without an interruption. No other initiator, even a high priority initiator, can interrupt this process. Subsequent write requests from the same initiator are held until the previous write transactions are completed to the external DDR memory. Subsequent write requests from other initiators can be accepted and allowed to write into WCB, but the DDR bridge does not write this data until the previous write transactions are completed to the external DDR memory.

## 1.3.3.2 Read Access Controller (Ask a Question)

The Read Access Controller (RAC) arbitrates read requests from read buffers and grants access to one of the requesting initiators depending on its priority. A round robin priority scheme is applied between Initiator Interface 0 and Initiator Interface 1. The RAC also routes the read data from the AXI target (FDDR) to the corresponding initiator based on the Read data ID.

#### 1.3.4 Locked Transactions (Ask a Question)

The DDR bridge initiators can initiate locked transfers by asserting the HMASTLOCK signal of the corresponding AHB interface. These locked transactions are initiated only after all the pending write and read transactions are completed.

The arbiter has a 20 bit up counter to detect a lock time-out condition. The counter starts counting when a locked transaction is initiated on the bus. When the counter reaches its maximum value, an interrupt is generated. The interrupt can be cleared by setting the DDR\_FIC\_LCKTOUT bit field in the DDR\_FIC\_SW\_HPB\_LOCKOUT\_SR register of the SYSREG block. If the interrupt is cleared and the lock signal is still asserted, the counter starts counting again. For more information, see Table 2-93.

The DDR bridge facilitates multiple AHB bus initiators to access a single AXI target and optimizes read and write operations from multiple AHB initiators to a single external DDR memory.

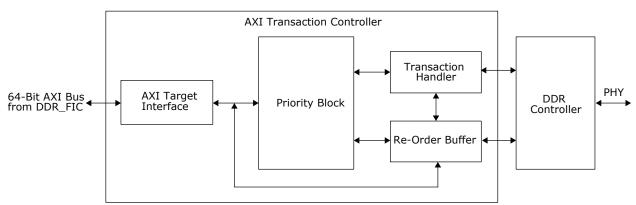

## 1.4 AXI Transaction Controller (Ask a Question)

The AXI transaction controller receives 64 bit AXI transactions from DDR\_FIC and translates them into DDR controller transactions. The following figure shows the block diagram of the AXI transaction controller interfaced with the DDR controller.

Figure 1-6. AXI Transaction Controller Block Diagram

The AXI transaction controller has four major blocks:

- AXI target interface

- Priority block

- Transaction handler

- Re-order buffer

## 1.4.1 AXI Target Interfaces (Ask a Question)

The AXI transaction controller has a 64 bit AXI target interface from DDR\_FIC. The AXI target port is 64 bits wide and is in compliance with the standard AXI protocol. Each transaction has an ID related to the initiator interface. Transactions with the same ID are completed in order while the transactions with different read IDs can be completed in any order depending on when the instruction is executed by the DDR controller. If a initiator requires ordering between the transactions, the same ID must be used.

The AXI target interface has individual read and write ports. The read port queues read AXI transactions and it can hold up to four read transactions. The write port handles only one write transaction at a time and generates the handshaking signals on the AXI interface.

## 1.4.2 Priority Block (Ask a Question)

The priority block prioritizes AXI read or write transactions and provides control to the transaction handler. AXI read transactions have a higher priority. The fabric initiator, using DDR\_FIC can be programmed to have a higher priority by configuring the PRIORITY\_ID and PRIORITY\_ENABLE\_BIT bit fields in the DDRC\_AXI\_FABRIC\_PRI\_ID\_CR register. For more information, see Table 2-76.

## 1.4.3 Transaction Handler (Ask a Question)

The transaction handler converts AXI transactions into DDR controller commands. The transaction handler works on a single transaction at a time from the read or write port queue that is selected by the priority block. The transaction handler has a write command controller and read command controller for write and read transactions.

The write command controller fetches the command from the AXI target write port and sends a write instruction to the DDR controller. If SECDED is enabled, a Read Modified Write (RMW) instruction is sent to the DDR controller. The read command controller generates read transactions to the DDR controller.

## 1.4.4 Re-Order Buffer (Ask a Question)

The re-order buffer receives data from the DDR controller and orders the data as requested by the AXI initiator when a single AXI transaction is split into multiple DDR controller transactions depending on the transfer size.

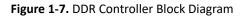

## 1.5 DDR Controller (Ask a Question)

The DDR controller receives requests from the AXI transaction controller, maps system addresses to DRAM addresses (rank, bank, row, and column), and prioritizes requests to minimize latency of reads (especially high priority reads) and maximize page hits. It also ensures that DRAM is properly initialized, all requests are made to DRAM legally (accounting for associated DRAM constraints), refreshes are inserted as required, and the DRAM enters, and exits various power-saving modes appropriately. The following figure shows the DDR controller connections in the FDDR subsystem.

The following sections describe the key functions of the DDR controller:

- Address mapping

- Transaction scheduling

- Write combine

- SECDED

- 1T 2T timing

- On-Die Termination (ODT) controls

- Performance

- DRAM constraints

## 1.5.1 Address Mapping (Ask a Question)

Read and write requests to the DDR controller requires a system address. The DDR controller maps this system address with the rank, bank, row, and column addresses to the DRAM.

The address mapper maps linear request addresses to the DDR memory addresses by selecting the source bit that maps to all the applicable DDR memory address bits. The address map interface registers can be configured to map the source address bits to the DRAM address.

Each DDR memory address bit has an associated register vector to determine its source. The source address bit number is determined by adding the internal base of a given register to the programmed value for that register, as shown in the following equation. [Internal base] + [register value] = [source address bit number]

For example, reading the description for REG\_DDRC\_ADDRMAP\_COL\_B3, the internal base is 3; so when the full data bus is in use, the column bit, 4 is determined by 3 + [register value]. For more information, see Table 2-10.

If this register is programmed to 2, then the source address bit is: 3 + 2 = 5.

The DDR Configurator assigns values to the address mapping registers depending on the selected number of columns, rows, and banks. The following figure provides the default mapping of the memory row, bank, and column address to the user interface address domain.

#### Figure 1-8. Address Mapping

| -                       | ••• |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-------------------------|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Full bus width mode     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| AXI/AHB Address         | 31  | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Row mapping (DDR2/DDR3) |     | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Row mapping (LPDDR)     |     |    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Bank mapping(DDR2/DDR3) |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 2  | 1  | 0  |    |    |   |   |   |   |   |   |   |   |   |   |

| Bank mapping(LPDDR)     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 1  | 0  |    |    |   |   |   |   |   |   |   |   |   |   |

| column mapping          |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 9  | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |   |

| Half bus width mode     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| AXI/AHB Address         | 31  | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Row mapping(DDR2/DDR3)  |     |    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Row mapping (LPDDR)     |     |    |    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Bank mapping(DDR2/DDR3) |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 2  | 1  | 0  |    |   |   |   |   |   |   |   |   |   |   |

| Bank mapping(LPDDR)     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 1  | 0  |    |   |   |   |   |   |   |   |   |   |   |

| column mapping          |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |   |

| Quarter bus width mode  |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                         |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| AXI/AHB Address         | 31  | 30 | 29 |    |    |    |    | _  | _  |    |    |    |    |    | _  | _  |    |    | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Row mapping(DDR2/DDR3)  |     |    |    | 15 | 14 |    |    |    |    |    | 8  | 7  |    | 5  |    |    | 2  |    | 0  |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Row mapping (LPDDR)     |     |    |    |    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |    |    |   |   |   |   |   |   |   |   |   |   |

| Bank mapping(DDR2/DDR3) |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 2  | 1  | 0  |   |   |   |   |   |   |   |   |   |   |

| Bank mapping(LPDDR)     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 1  | 0  |   |   |   |   |   |   |   |   |   |   |

| column mapping          |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Following is the list of address mapping registers.

- DDRC\_ADDR\_MAP\_BANK\_CR

- DDRC\_ADDR\_MAP\_COL\_1\_CR

- DDRC\_ADDR\_MAP\_COL\_2\_CR

- DDRC\_ADDR\_MAP\_COL\_3\_CR

- DDRC\_ADDR\_MAP\_ROW\_1\_CR

- DDRC\_ADDR\_MAP\_ROW\_2\_CR

While configuring the registers, ensure that two DDR memory address bits are not determined by the same source address bit.

## Important:

- Some registers map to multiple source address bits (REG\_DDRC\_ADDRMAP\_ROW\_B0\_11).

- For the DDR controller to arrive at the right address, FDDR maps the system address or AXI address bits [4:0].

- In full bus width mode, the system address bits [4:0] are used to map the lower column address bits—C0, C1, and C2.

- In half bus width mode, the system address bits [4:0] are used to map the lower column address bits—C0, C1, C2, and C3.

- In quarter bus width mode, the system address bits [4:0] are used to map the lower column address bits—C0, C1, C2, C3, and C4.

The FDDR configurator uses {Row, Bank, Column} address mapping as shown in the following example.

## **1.5.1.1** Example: FDDR Configurator Address Map Configuration (Ask a Question)

In this example, the address map registers are configured to access a 512 MB DDR3 SDRAM memory, MT41J512M8RA, from the FDDR subsystem. 1.10.2. Example 2: Connecting 32 Bit DDR3 to FDDR\_PADs with SECDED shows the connections between the 32-bit DDR3 memory to FDDR\_PADs with SECDED. The 512M x 8 bit DDR3 memory module has 3 Bank Address lines, 16 rows, and 10 columns.

- The column address bits 3 to 9 are mapped from the system address bit[5] to system address bit[11]. To map the column 3 bit (C3) to address [5], the field is configured to 3, as the base value is 2. Similarly, the other column address bits are configured as follows:

- DDRC\_ADDR\_MAP\_COL\_1\_CR = 0x3333

- DDRC\_ADDR\_MAP\_COL\_2\_CR = 0x3FFF

- DDRC\_ADDR\_MAP\_COL\_3\_CR = 0x3300

- The bank address bit 0 to 2 are mapped to system address bit[12] to system address bit[14]. To map the bank bit 0 to address [12], the field is configured to A, as the base value is 2. Similarly, the other bank address bits are configured as follows:

- DDRC\_ADDR\_MAP\_BANK\_CR = 0xAAA

- The row address bits 0 to 15 are mapped to system address bit[15] to system address bit[27]. To map the bank bit0 to address [15], the field is configured to 9, as the base value is 6. Similarly, the other bank address bits are configured as follows:

- DDRC\_ADDR\_MAP\_ROW\_1\_CR = 0x9999

- DDRC\_ADDR\_MAP\_ROW\_2\_CR = 0x9FF

**Important:** The FDDR subsystem can access the 2 GB address space (0x00000000 - 0x7FFFFFF). But in this example, 512 MB (0x00000000 - 0x1FFFFFF) DDR3 SDRAM is connected to the 16 address lines of FDDR. The memory visible in the other memory space is a mirror of this 512 MB memory.

## 1.5.2 Transaction Scheduling (Ask a Question)

The controller optimizes read and write requests to minimize the DDR read and write latencies using a 16-location Content Addressable Memory (CAM) that stores outstanding requests. The DDR controller schedules the read and write transactions to the DDR memory. Based on the commands from the AXI transaction controller, the transitions are classified in to three types:

- Low-Priority Reads (LPR)

- High-Priority Reads (HPR)

- Writes (WR)

Each type of transaction has a queue and the queued transactions can be in normal state or in critical state. The transactions in a queue moves from normal state to critical state when that transaction is not serviced for a count of MAX\_STARVE\_X32 clocks. The MAX\_STARVE\_X32 values for each queue can be configured using the DDR controller performance registers. For more information, see 1.9. Functional Timing Diagrams. The DDR controller completes the critical transactions with a high priority.

## 1.5.3 Write Combine (Ask a Question)

The DDR controller combines multiple writes to the same address into a single write to the DDR memory. When a new write encounters the queued write, the DDR controller overwrites

the queued write data with the new write data and performs only a single write transaction. To disable the write combine set of the register the bits from the REG\_DDRC\_DIS\_WC field of the DDRC\_ADDR\_MAP\_COL\_3\_CR register is set to 1. For more information, see Table 2-31.

#### 1.5.4 SECDED (Ask a Question)

The DDR controller supports built-in SECDED capability for correcting single-bit errors and detecting two-bit errors. The SECDED feature can be enabled in the DDR memory controller configuration window. When SECDED is enabled, the DDR controller adds 8 bits of SECDED data to every 64 bits of data. Enabling SECDED might cause a reduction in throughput.

For 64-bit aligned addressing. the SECDED feature corrects all the errors only when memory selection parameters listed in Table 1-11 are followed. For an x32 interface, if the AXI interface width is 64 bit, the maximum supported burst length is four for correcting all the single bit errors and for detecting double bit errors.

The DDR controller computes ECC for every 64 bit data. When SECDED is enabled, a write operation computes and stores a SECDED code with the data, and a read operation reads and checks the data against the stored SECDED code. It is, therefore, possible to receive single/dual bit errors when reading uninitialized memory locations. To avoid this, all the memory locations must be written before being read.

For a non 64-bit write operation the DDR controller performs 256 bit Read Modify Write (RMW) operation. This read modify write operation is always performed on 256 bit aligned addresses. For example, if DDR controller receives a 32 bit write operation to address 0x4, then the DDR controller performs the following operations:

- Reads the 256 bit data from 0x0 (256 bit aligned address for 0x4)

- Modifies 32 bits (bit 33 to bit 64) of that 256 bit data with the user's 32 bit data

- Computes the ECC and writes 288 bits (256 bit data + 32 bit ECC) to address 0x0

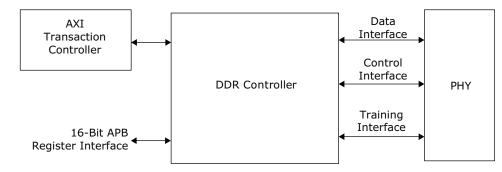

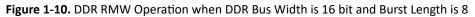

The following figure shows the DDR controller burst transactions to DRAM for unaligned 64 bit AXI write transaction. The DDR controller is configured for DDR3 memory, 32 bit burst width, and burst length 8.

| MDDR signals<br>MDDR_RESET_N 1                | -          |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

|-----------------------------------------------|------------|-------------------|---------|----------|------|---|----|-----|------|-------|--------|---|----|------|----|--------------|---------------|--------------|-------|----|------|--|-----|-----|-----|-----|-------|--------|-------|-------|

| MDDR_CKE 0                                    |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| 4 MDDR_CLK 1                                  |            |                   |         | $\neg d$ | undr |   | ΠĤ |     |      | i n l |        |   | hп |      | hc |              | hп            |              |       | nп |      |  | n c | ini | h n | n d | i m l |        |       |       |

| MDDR_CS_N 1                                   |            |                   |         |          |      |   |    | - 4 |      |       | 5      |   |    | ÌГ   | -  |              |               |              |       |    | <br> |  |     |     | n n |     |       |        |       |       |

| E-C MODR_BA 1                                 |            | 1                 |         |          |      |   |    | Xò  |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| MDDR_RAS_N 1                                  |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| MDDR_CAS_N 1                                  |            |                   |         |          |      |   |    |     |      |       |        |   |    | ī    |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| A MODR_WE_N 1                                 |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     | ٦   |     |       |        |       |       |

| D-400 0400                                    | )          | 0400              |         |          |      |   |    |     |      |       | ( 0000 |   |    | 0008 |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| E-4 MDDR_DQ 222222                            | 2222       |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       | 0     |

| E-4 MDDR_DQS z                                |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              | (0            |              | ( 1 ) |    |      |  |     |     |     |     |       |        |       |       |

| 🖬 👍 MDDR_DM_RDQS z                            |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       | 0      |       | ()    |

| E-4 MDDR_DQ_ECC z                             |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       | _  |      |  |     |     |     |     |       | 0      | _     |       |

| A MDDR_DQS_ECC z                              |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       | ي ا ا |

| - AND IF                                      |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    | A 1.4        | huret         | read         |       |    |      |  |     |     |     | DR. | M b   | urst v | vrite | _     |

| CLK     0     0     00000     00000     00000 | 00066      |                   |         |          |      |   |    |     |      |       |        | L |    |      | 4  | <b>V</b> uvi | <b>Pul</b> st | <u>lea</u> u |       |    |      |  |     |     |     |     |       |        |       |       |

| D-4 AWLEN f                                   | 0055       | 00000             | 020     |          |      | _ |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       | _      |       |       |

| B-AWLEN T<br>B-AWSIZE 3                       |            |                   |         |          |      | _ |    | _   | _    |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| P-4 AWLOCK 0                                  |            | 0 ) <u>3</u><br>0 |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| D-4 AWBURST 1                                 |            | 0<br>1 1          |         |          |      | _ |    | _   |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| AWVALID 0                                     |            | × (*              |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| AWREADY 1                                     |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| of VISTRB Of                                  |            | 00                | fof     |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     | _     |        |       |       |

| 🚽 wlast 🛛 0                                   |            |                   |         | 1        |      |   |    |     | AXII | 32-bi | t writ | e |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| 💪 WVALID 0                                    |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| n 🕹 WDATA feffff                              | 1111111809 | 000000000         | (feffff | 111      |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| s wready 1                                    |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| E-4 BRESP 0                                   |            | o                 |         |          |      |   |    |     |      | _     |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| svalid 0                                      |            |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

| 👍 BREADY 0                                    | -          |                   |         |          |      |   |    |     |      |       |        |   |    |      |    |              |               |              |       |    |      |  |     |     |     |     |       |        |       |       |

Figure 1-9. DDR RMW Operation when DDR Bus Width is 32 bit and Burst Length is 8

The following figure shows the DDR controller burst transactions to DRAM for unaligned 64 bit AXI write transaction. The DDR controller is configured for DDR3 memory, 16 bit bust width, and burst length 8.

The following figure shows the DDR controller burst transactions to DRAM for unaligned 64 bit AXI write transaction. The DDR controller is configured for DDR3 memory, 8 bit bust width, and burst length 8.

#### Figure 1-11. DDR RMW Operation when DDR Bus Width is 8 bit and Burst Length is 8

The SECDED bits are interlaced with the data bits. The following table lists the SECDED DQ lines at FDDR memory.

#### Table 1-1. SECDED DQ Lines at FDDR Memory

| Mode                   | SECDED Data Pins |

|------------------------|------------------|

| Full bus width mode    | FDDR_DQ_ECC[3:0] |

| Half bus width mode    | FDDR_DQ_ECC[1:0] |

| Quarter bus width mode | FDDR_DQ_ECC[0]   |

When the controller detects a correctable SECDED error, it does the following:

- Generates an interrupt signal which can be monitored by reading the interrupt status register, DDRC\_ECC\_INT\_SR. The FDDR subsystem also generates the ECCINT interrupt signal that can be monitored from the FPGA fabric.

- Sends the corrected data to the read requested FPGA fabric initiator as part of the read data.

- Sends the SECDED error information to the DDRC\_LCE\_SYNDROME\_1\_SR register.

- Performs a read-modify-write operation to correct the data present in the DRAM.

When the controller detects an uncorrectable error, it does the following:

- Generates an interrupt signal which can be monitored by reading the interrupt status register, DDRC\_ECC\_INT\_SR. The FDDR subsystem also generates the ECCINT interrupt signal that can be monitored from the FPGA fabric.

- Sends the data with error to the read requested FPGA fabric initiator as part of the read data.

- Sends the SECDED error information to the DDRC\_LUE\_SYNDROME\_1\_SR register.

The following SECDED registers can be monitored for identifying the exact location of an error in the DDR SDRAM:

- DDRC\_LUE\_ADDRESS\_1\_SR and DDRC\_LUE\_ADDRESS\_2\_SR give the row/bank/column information of the SECDED unrecoverable error.

- DDRC\_LCE\_ADDRESS\_1\_SR and DDRC\_LCE\_ADDRESS\_2\_SR give the row/bank/column information of the SECDED error correction.

- DDRC\_LCB\_NUMBER\_SR indicates the location of the bit that caused the single-bit error in the SECDED case (encoded value).

- DDRC\_ECC\_INT\_SR indicates whether the SECDED interrupt is because of a single-bit error or double-bit error. The SECDED interrupt and the ECC interrupt can be cleared by writing 1 to FDDR\_INTERRUPT\_SR (0x53C).

**Important:** Uncorrectable 2-bit errors trigger a HRESP error exception to the master (system/CPU/Mi-V). The HRESP error exception prevents the corrupt data from triggering an unexpected event or response at the master. Therefore, the master must implement a bus exception handler routine to recover or reset from a memory error.

## 1.5.5 1T or 2T Timing (Ask a Question)

To use the DRAM in 1T or 2T Timing modes, configure the DDRC\_PERF\_PARAM\_3\_CR register. To clock the address bus, use the 1T or 2T clocking. In 1T, the DDR controller can issue a new command on every clock cycle. In 2T timing, the DDR controller holds the address and command bus valid for two clock cycles. This reduces the efficiency of the bus to one command per two clocks, but it doubles the amount of setup and hold time. The data bus remains the same for all of the variations in the address bus. Default configuration is 1T timing mode.

## 1.5.6 ODT Controls (Ask a Question)

To enable or disable the ODT for a specific rank of memory, configure the DDRC\_ODT\_PARAM\_1\_CR and DDRC\_ODT\_PARAM\_2\_CR registers. These registers must be configured before taking the controller out of soft reset. They are applied to every read or write issued by the controller.

#### 1.5.7 Performance (Ask a Question)

The DDR controller has several performance registers that can be used to increase the speed of the read and write transactions to the DDR memory.

The DDR controller has a transaction store, shared for low and high priority transactions. The DDRC\_PERF\_PARAM\_1\_CR register can be configured for allocating the transaction store between the low and high priority transactions. For example, if the REG\_DDRC\_LPR\_NUM\_ENTRIES field is configured to 0, the controller allocates more time to high priority transactions. The ratio for LPR: HPR is 1:7 as the transaction store depth is 8. For more information, see Table 2-40.

The DDRC\_HPR\_QUEUE\_PARAM\_1\_CR, DDRC\_LPR\_QUEUE\_PARAM\_1\_CR, and DDRC\_WR\_QUEUE\_PARAM\_CR registers can be configured for the minimum clock values for treating the transactions in the HPR, LPR, and WR queues as critical and non-critical.

To force all incoming transactions to low priority, configure the DDRC\_PERF\_PARAM\_2\_CR register. By default, it is configured to force all the incoming transactions to low priority.

## 1.5.8 Dynamic DRAM Constraints (Ask a Question)

Timing parameters for DDR memories must be configured according to the DDR memory specification. Dynamic DRAM constraints are divided into three basic categories:

- **Bank Constraints**: Affect the transactions that are scheduled to a given bank

- Rank Constraints: Affect the transactions that are scheduled to a given rank

- Global Constraints: Affect all transactions

## 1.5.8.1 Dynamic DRAM Bank Constraints (Ask a Question)

The following table lists the timing constraints that affect the transactions to a bank. The control bit field must be configured according to the DDR memory vendor specification.

| Timing Constraint of DDR<br>Memory                   | Control Bit        | Description                                                                                                                                                                                               |

|------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Row cycle time (t <sub>RC</sub> )                    | REG_DDRC_T_RC      | Minimum time between two successive cycles activates to a given bank. For more information, see Table 2-21.                                                                                               |

| Row precharge command period (t <sub>RP</sub> )      | REG_DDRC_T_RP      | Minimum time from a precharge command to the next command affecting that bank. For more information, see Table 2-28.                                                                                      |

| Minimum bank active time<br>(t <sub>RAS(min)</sub> ) | REG_DDRC_T_RAS_MIN | Minimum time from an activate command to a precharge command to the same bank. For more information, see Table 2-25.                                                                                      |

| Maximum bank active time<br>(t <sub>RAS(max)</sub> ) | REG_DDRC_T_RAS_MAX | Maximum time from an activate command to a precharge command to the same bank. For more information, see Table 2-25.                                                                                      |

| RAS-to-CAS delay (t <sub>RCD</sub> )                 | REG_DDRC_T_RCD     | Minimum time from an activate command to a Read or Write command to the same bank. For more information, see Table 2-28.                                                                                  |

| Write command period ( $t_{WR}$ )                    | REG_DDRC_WR2PRE    | Minimum time from a Write command to a precharge command to the same bank. For more information, see Table 2-23.                                                                                          |

| Read-to-precharge delay<br>(t <sub>RTP</sub> )       | REG_DDRC_RD2PRE    | Minimum time from a Read command to a precharge<br>command to the same bank.<br>Set this to the current value of additive latency plus half of<br>the burst length. For more information, see Table 2-23. |

#### Table 1-2. Dynamically Enforced Bank Constraints

## 1.5.8.2 Dynamic DRAM Rank Constraints (Ask a Question)

The following table shows the timing constraints that affect the transactions to a rank. The control bit field must be configured according to the DDR memory vendor specification.

| Timing Constraints of DDR<br>Memory                                          | Control Bit            | Description                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nominal refresh cycle time<br>(t <sub>RFC</sub> (nom) or t <sub>REFI</sub> ) | REG_DDRC_T_RFC_NOM_X32 | Average time between refreshes for a given rank. The actual time between any two refresh commands could be longer or shorter than this; this represents the maximum time allowed between refresh commands to a given rank when averaged over a large period of time. For more information, see Table 2-6. |

| Minimum refresh cycle<br>time t <sub>RFC(min)</sub>                          | REG_DDRC_T_RFC_MIN     | Minimum time between refreshes or activations. For more information, see Table 2-5.                                                                                                                                                                                                                       |

Table 1-3. Dynamically Enforced Rank Constraints

#### .....continued

| Timing Constraints of DDR<br>Memory    | Control Bit    | Description                                                                                                                                                                                |  |  |  |  |

|----------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RAS-to-RAS delay (t <sub>RRD</sub> )   | REG_DDRC_T_RRD | Minimum time between activations from bank A to bank<br>B. For more information, see Table 2-28.                                                                                           |  |  |  |  |

| RAS-to-CAS delay (t <sub>CCD</sub> )   | REG_DDRC_T_CCD | Minimum time between two reads or two writes (from bank A to bank B). For more information, see Table 2-28.                                                                                |  |  |  |  |

| Four active window (t <sub>FAW</sub> ) | REG_DDRC_T_FAW | Sliding time window in which a maximum of 4 bank<br>activations are allowed in an 8-bank design. In a<br>4-bank design, set this register to 0x1. For more<br>information, see Table 2-21. |  |  |  |  |

#### 1.5.8.3 Dynamic DRAM Global Constraints (Ask a Question)

The following table lists the timing constraints that affect the global transactions. The control bit field must be configured according to the DDR memory vendor specification.

| ble 1-4. Dynamic DRAM Global Constraints |

|------------------------------------------|

|------------------------------------------|

| Timing Constraint             | Control Bit            | Description                                                                                                                 |  |

|-------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Read-to-write turnaround time | REG_DDRC_RD2WR         | Minimum time to allow between issuing any Read command and WRITE command. For more information, see Table 2-26.             |  |

| Write-to-read turnaround time | REG_DDRC_WR2RD         | Minimum time to allow between issuing any Write command and issuing any Read command. For more information, see Table 2-26. |  |

| Write latency                 | REG_DDRC_WRITE_LATENCY | Time between write command and write data to DRAM.<br>For more information, see Table 2-22.                                 |  |

The DDR memories require delays after initializing the mode registers. The following registers must be configured for delay requirements for the DDR memories. The DDR controller uses these delay values while initializing the DDR memories.

- DDRC\_CKE\_RSTN\_CYCLES\_1\_CR. Recommended value is 0x4242. For more information, see Table 2-15.

- DDRC\_ CKE\_RSTN\_CYCLES\_2\_CR. Recommended value is 0x8. For more information, see Table 2-16.

## 1.6 DDR PHY (Ask a Question)

DDR PHY provides a physical interface to DDR2, DDR3, and LPDDR1 SDRAM devices. It receives commands from the DDR controller and generates DDR memory signals required to access the external DDR memory.

The PHY adjusts the delay between the data (DQ) lines and DQS signals by using a separate DLL for each data slice. DDR has 36 DQ lines split into the following data slices:

- Data slice0: DQ0 DQ7

- Data slice1: DQ8 DQ15

- Data slice2: DQ16 DQ23

- Data slice3: DQ24 DQ31

- Data slice4: DQ32 DQ35

## 1.7 Initialization (Ask a Question)

Before the FDDR subsystem becomes active, it goes through an initialization phase, which includes reset sequence, ZQ calibration, DRAM training, and memory initialization.

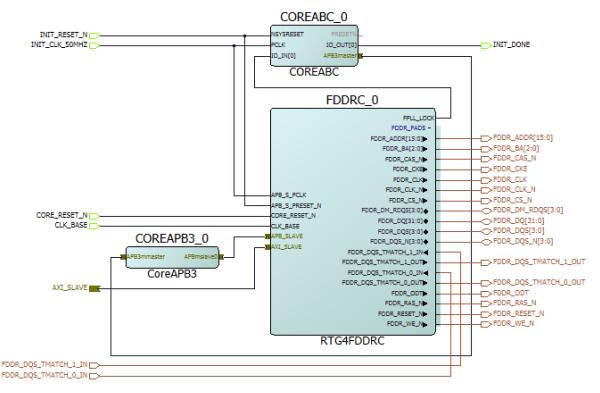

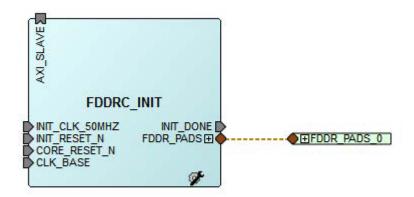

The FDDR controller registers must also be initialized via the APB configuration interface. When using the FDDR Controller (FDDRC) with Initialization, the FDDR core is automatically initialized with the desired user settings via an auto-instantiated CoreABC IP core.

## 1.7.1 CoreABC Initialization Sequence (Ask a Question)

The FDDR with initialization IP (RTG4FDDRC\_INIT) includes a built-in CoreABC for configuring the FDDRC registers and initializing FDDRC.

During initialization, CoreABC implements the following:

- Performs APB writes to set the FDDR PLL (FPLL) VCO to high frequency range.

- Issues the PLL reset to allow the VCO to calibrate to a high gain setting.

- Performs APB writes to restore the required FPLL frequency.

- Waits for the FPLL to Lock.

- Resumes initialization of FDDRC registers as per the user settings.

For more information about the FDDR initialization state machine, see RTG4 DDR Memory Controller with Initialization Configuration User Guide.

## 1.7.2 Guidelines for FDDR with Built-In CoreABC (Ask a Question)

The following points must be considered for proper FDDR initialization:

- If the reference clock (CLK\_BASE) to the FDDR FPLL is sourced from an RTG4 Fabric CCC (FCCC) with enhanced PLL calibration, then the user must keep the FDDR with Initialization INIT\_RESET\_N input asserted until the fabric PLL lock has been acquired. This will prevent the FPLL calibration sequence and FDDR initialization from proceeding prior to achieving a stable reference clock. Figure 1-13 shows the FDDR and CoreABC SmartDesign connections.

- If the release of INIT\_RESET\_N can't be directly connected to the Fabric PLL Lock output (when the FCCC supplies the FDDR CLK\_BASE), the CoreABC program instructions can be manually updated to delay the FDDR initialization process. This delay can be achieved using any one of the following methods.

- Assert the FPLL power-down at the start of the CoreABC code sequence (using APBWRT DAT16 0 0x1508 0x32e4). Then, using an additional IO input to CoreABC, poll for the fabric PLL Lock to go high (using WAIT UNTIL INPUT#). Then, deassert the FPLL POWERDOWN (using APBWRT DAT16 0 0x1508 0x12e4).

- Add a wait state at the start of the CoreABC init code to wait for the max FCCC PLL lock acquisition time (500 μs) + ~160 μs fabric PLL calibration time, before allowing the FDDR CoreABC initialization sequence to run.

| <b>1</b> -1-2 |  |

|---------------|--|

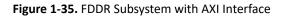

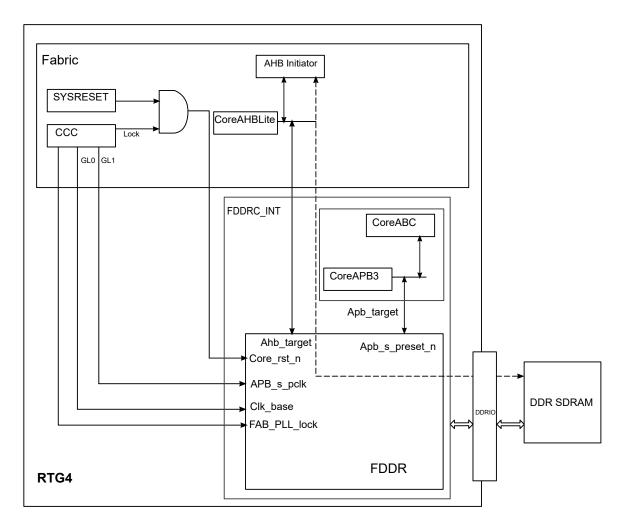

**Tip:** The CoreABC program instructions can be updated on the **Program** tab of the CoreABC Configurator, as shown in Figure 1-12.

Figure 1-12. CoreABC Program Tab

```

Parameters Program Analysis

// -----

^

// CoreABC FDDR Initialization Sequence

11 --

// Allow time for the APB interface to be ready a

NOP

NOP

NOP

// actual_ref_div = 2

// actual_fb_div = 2

// actual_vco_div = 8

// actual_vco_freq = 800

// highvco_ref_div = 2

// highvco_fb_div = 3

// highvco_vco_div = 8

// highvco_vco_freq= 1200

// Assert FPLL internal feedback mode (PLL CONFIG

APBWRT DAT16 0 0x1508 0x12e4

// PLL_CONFIG_LOW_2 for high vco config (set to 1

APBWRT DAT16 0 0x1504 0x60

// PLL_CONFIG_LOW_1 for high vco configuration

APBWRT DAT16 0 0x1500 0x81

// PLL_CONFIG_LOW_2 for high vco configuration

APBWRT DAT16 0 0x1504 0x63

// Assert FPLL POWERDOWN (PLL_CONFIG_HIGH:PLL_PD=

APBWRT DAT16 0 0x1508 0x32e4

Format Analyze program as I type

ОК

Cancel

```

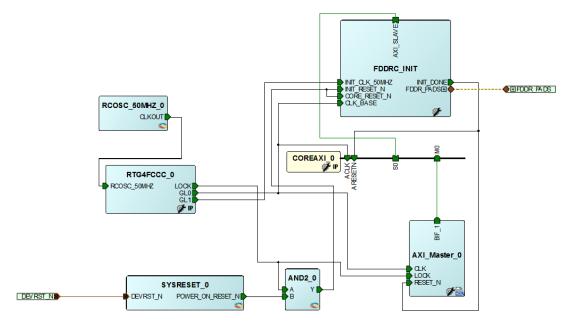

#### Figure 1-13. FDDR Initialization Connection

## 1.7.3 Reset Sequence (Ask a Question)

The following figure shows the reset sequence required for the FDDR subsystem from the power-onreset stage. Once the CORE\_RESET\_N signal of the FDDR subsystem is asserted, the FPLL\_LOCK signal is asserted and the APB register configuration is complete. Assertion of CORE\_RESET\_N denotes the end of the reset sequence. The DDR controller performs external DRAM memory reset and initialization according to the JEDEC specification, including reset, refresh, and mode registers. For more information about Reset sequence see AN4752: Interfacing RTG4 with External DDR3 Memory.

**Important:** The REG\_DDRC\_SOFT\_RSTB bit of the DDRC\_DYN\_SOFT\_RESET\_CR register can be set to 0 to reset the DDR controller. To release the DDR controller from reset, set the REG\_DDRC\_SOFT\_RSTB bit of the DDRC\_DYN\_SOFT\_RESET\_ALIAS\_CR register to 1.

#### 1.7.3.1 DDR I/O Calibration (Ask a Question)

Each DDR I/O has an ODT feature; the ODT is calibrated depending on the DDR I/O standard. DDR I/O calibration occurs after the DDR I/Os are enabled. I/O calibration is always enabled when the DDR subsystem is configured for DDR2 and DDR3 memories. I/O calibration can be optionally disabled when controller is configured to LPDDR. If I/O calibration is enabled, all I/Os in the DDR bank are calibrated even if the DDR controller does not use all I/Os in the bank. For more information on DDR I/O calibration, see the UG0741: RTG4 FPGA I/O User Guide.

#### Figure 1-14. Reset Sequence

| PO_RESET_N                         |  |

|------------------------------------|--|

| APB_S_PRESET_N                     |  |

| DDRIO Calibration                  |  |

| CORE_RESET_N .                     |  |

| FPLL_LOCK                          |  |

| FDDR APB Register<br>Configuration |  |

#### 1.7.4 ZQ Calibration (Ask a Question)

ZQ calibration is applicable only for DDR3. It is used to calibrate the DRAM output drivers ( $R_{ON}$ ) and ODT values. DDR3 SDRAM requires a longer time to calibrate  $R_{ON}$  and ODT at initialization and a relatively lesser time to perform periodic calibrations.

The DDR controller performs ZQ calibration by issuing a ZQ Calibration Long (ZQCL) command and ZQ Calibration Short (ZQCS) command.

ZQCL is used to perform initial calibration during the power-up initialization sequence. This command is allowed for a period of  $t_{ZQinit}$ , as specified by a memory vendor that you use. The value of  $t_{ZQinit}$  can be modified using the register bits, REG\_DDRC\_T\_ZQ\_LONG\_NOP. For more information, see Table 2-36.

The ZQCS command is used to perform periodic calibration to account for voltage and temperature variations. A shorter timing window is provided to perform calibration and transfer of values as defined by timing parameter  $t_{ZQCS}$ . The  $t_{ZQCS}$  parameter can be modified using the register bits, REG\_DDRC\_T\_ZQ\_SHORT\_NOP. For more information, see Table 2-37. Other activities are not performed by the controller for the duration of  $t_{ZQinit}$  and  $t_{ZQCS}$ . All DRAM banks are precharged and  $t_{RP}$  is met before the ZQCL or ZQCS command is issued by the DDR controller.

## 1.7.5 DRAM Training (Ask a Question)

High-Speed DDR3 memories typically require the DDR controller to implement Write-Leveling, Read DQS Gate Training, and Read Data Eye Training. However, the RTG4 FDDR only supports a maximum data rate of 333 MHz/667 Mbps, which means the clock period and data window are relatively large compared to high-speed DDR3 memory interfaces. Therefore, dynamic write-leveling and read training are not performed. The following sections describe how write-leveling and read training are addressed by RTG4 FDDR.

#### 1.7.5.1 Write-Leveling (Ask a Question)

Dynamic write-leveling is not required for the RTG4 FDDR controller. The board layout need to follow the guidelines as per the AC439: RTG4 FPGAs Board Design and Layout Guidelines to keep the skew between DQS and CK within the JEDEC DDR3 t<sub>DOSS</sub> limit of ±750 ps at each memory device.

For board layouts, which do not meet the RTG4 Board Design Guidelines, the RTG4 FDDR controller allows static delay ratios which delays DQS for each byte lane so that the skew between DQS and CK is kept within JEDEC limits. REG\_PHY\_WR\_DQS\_SLAVE\_RATIO [49:0] is split across four registers called PHY\_WR\_DQS\_SLAVE\_RATIO\_#\_CR, where # ranges from 1 to 4. The 50 bit ratio value is allocated to five write DQS delay ratios so that each data slice can have its DQS delayed independently as follows:

- [9:0] for DQS0

- [19:10] for DQS1

- [29:20] for DQS2

- [39:30] for DQS3

- [49:40] for DQS4

Each 10 bit ratio value is calculated using the following formula to delay DQS by the DELAY value in picoseconds (ps):

Ratio = (DELAY (in ps) \* 256) / DDR3\_CLK\_PERIOD (in ps)

#### 1.7.5.2 Read-Leveling (Ask a Question)

RTG4 FDDR does not perform the dynamic Read DQS Gate Training and Data Eye Training. Instead, these functions are achieved by using built-in static delay values automatically generated by Libero SoC for the FDDR automatic register initialization.

#### 1.7.5.3 Read Gate (Ask a Question)

The DQS gate is aligned by the Libero SoC auto-generated FDDR initialization code containing fixed delay ratios to account for board round-trip time between RTG4 and the DDR3 memory. The TMATCH\_OUT and TMATCH\_IN signals are shortened close to the FPGA balls to remove the RTG4 output and input delays from the round-trip delay time. Therefore, the fixed delay ratios represent only the board delay.

The fixed delay ratios work in combination with board layouts which follows the AC439: RTG4 FPGAs Board Design and Layout Guidelines.

## 1.7.5.4 DQS Alignment within Data Eye (Ask a Question)

The incoming read DQS is internally centered within the read DQ data window using a static delay ratio. This static delay is applied by the Libero SoC auto-generated FDDR initialization code. The fixed delay ratios work in combination with board layouts, which follow the AC439: RTG4 FPGAs Board Design and Layout Guidelines.

**Tip:** The Libero SOC auto-generated delay ratio for read DQS data eye centering is written to the required register.

#### 1.7.6 DDR Memory Initialization Time (Ask a Question)

The time to initialize the DDR memory depends on the following factors:

- · Power-up and register initialization by System Controller

- DDR controller and PHY configuration registers initialization by CoreABC

- DDR memory initialization by DDR controller according to JEDEC standard (mode register configuration and training)

- DDR memory settling time configured in the DDR memory controller configuration window

#### Important:

- If the reference clock (CLK\_BASE) to the FDDR FPLL is sourced from RTG4 FCCC with an enhanced PLL Calibration, you must stagger the release of the FDDR initialization with INIT\_RESET\_N until the fabric PLL lock is asserted. This ensures that the reference clock is stabilized before the FPLL calibration and FDDR initialization.

- If you cannot stagger the INIT\_RESET\_N release until the fabric PLL is locked, the FDDR initialization with underlying SmartDesign connections and CoreABC code can be modified to any one of the following:

- Assert FPLL Power Down at the start of the CoreABC code sequence. Release the FPLL from Power Down and let the generated initialization sequence run after the fabric PLL lock is signaled by an added I/O Input to CoreABC connected to the fabric PLL lock output. For further details, see Example.

- Add a wait state at the start of the CoreABC init code to wait for the maximum PLL lock acquisition time (500 μs + ~150 μs fabric PLL calibration time) before allowing the FDDR CoreABC initialization sequence to run. For further details, see Figure 1-15

#### Figure 1-15. FDDR Initialization Using CoreABC

#### For example

CoreABC sequence to add at the start of the init code:

Some CoreABC init code at the start of the sequence to initially put the FPLL into POWERDOWN mode (APBWRT DAT16 0 0x1508 0x32e4).

- Poll for the fabric PLL Lock to go high (WAIT UNTIL INPUT#)

- De-assert the FPLL POWERDOWN (APBWRT DAT16 0 0x1508 0x12e4)

Follow the enhanced CoreABC init code generated by v12.4 FDDR with the Init core.

## 1.8 FDDR Subsystem Ports (Ask a Question)

The following figure shows the DDR controller ports categorized into the following sub-categories:

- **CLK and Reset Signal**: Clock and reset signals required for the FDDR.

- **Interrupts**: FDDR has five interrupts to interrupt you logic to indicate the ECC error, PLL lock, and so on.

- **AXI Target Interface**: Signals required when the DDR controller is configured in AXI mode. To perform DDR memory transactions, an AXI initiator is implemented in the FPGA fabric logic interfaces with the DDR controller.

- **AHB0/AHB1 Target Interface**: Signals required when the DDR controller is configured in AHB mode. To perform DDR memory transactions, an AHB initiator is implemented in the FPGA fabric logic interfaces with the DDR Controller.

- **APB Interface**: Allows user logic or software to configure the DDR controller.

- **SDRAM Interface**: Signals are connected to the SDRAM.

Figure 1-16. DDR Controller Port List

The following tables list the signals for each of the interfaces.

| Signal Name       | Туре | Polarity | Description                                                                                                                                          |  |